# Real Time Implementation of Integer DCT based Video Watermarking Architecture

Amit Joshi<sup>1</sup>, Vivekanand Mishra<sup>2</sup>, and Rajendra Patrikar<sup>3</sup>

<sup>1</sup>Electronics and Communication Department, Malaviya National Institute of Technology, India <sup>2</sup>Electronics Engineering Department, Sardar Vallabhbhai National Institute of Technology, India <sup>3</sup>Electronics and Communication Department, Visvesvaraya National Institute of Technology, India

**Abstract**: With the recent development in multimedia communication network, data integrity and security of original content is the area of concern. Video is the one of the most popular object which is being shared easily throughout the media. Video watermarking is the current state of research to resolve the video ownership and authenticity related issues. There is a substantial amount of development in software based video watermarking from last few years. The prior works mainly focused on video watermarking that targeted for raw video where the watermark is embedded on the uncompressed video. At the present video capturing devices produce their output in one of the video compression standard. Software watermarking introduces a measurable quantity of delay between video capturing and watermark embedding process. Thus, software watermarking is not one of the ideal choices for real time watermarking has been proposed. The proposed video watermarking is developed for real time watermark embedding and can easily be adapted as primary part of H.264 encoder. The proposed algorithm has an essential part in form of integer DCT. Integer DCT is implemented with two different approaches, one is with fully pipeline architecture and the other is recursive architecture, for better speed and area optimization. The robustness of the algorithm has been improved against some video attacks with introducing the concept of scene change detection.

Keywords: H.264, integer DCT, parallel processing, real time watermarking, recursive architecture.

Received May 17, 2013; accepted November 10, 2013; published online August 9, 2015

## **1. Introduction**

Digital video is an essential multimedia object which is transmitted through the channel [3]. The transmission of digital content has also imparted a challenge of secure communication from source to destination [17]. Digital video watermarking is the intelligent way of hiding owner's credential to prove the claim of ownership. H.264 is a block-oriented video compression standard which is jointly developed by ITU-T Video Coding Experts Group (VCEG) and ISO/IEC JTC Moving Picture Experts Group (MPEG) [1]. H.264 (MPEG-4 Part 10 advanced), is the latest standard and is developed for high quality video for low bit rate application devices like mobile phones. PDA etc., [19]. It has better quality as good as twice or four times compared to all previous video standards while having almost half of the bandwidth [10].

There are some commercial applications like video conference, movie production and video recording, video broadcasting system, where a real-time watermarking is the essential requirement [2, 7]. In such scenario, the software solution is not recommended because of the involvement of the delay between capturing the video and transmission over the channel [5]. There is a need to develop the custom hardware which resides in the electronics compliances such that watermark is embedded at the same time when it is being captured [12]. The real time embedding of the watermark can be done on raw

video and along with the compression standard. With the demand of the applications, the bandwidth and data rates are challenging task for uncompressed or raw video. The compressed video watermarking satisfies the requirement of security at lesser bandwidth [6]. The present video capturing devices like mobile phones, digital camera, etc., are produced output in one of the compression standard [28]. Video compression systems operating at high speed and good quality requires efficient hardware architecture with high throughput for area and power optimization [21]. In the paper, real-time video watermarking algorithm for H.264 is explained. H.264 is standard which is based on integer arithmetic computation [22, 27]. Integer Discrete Cosine Transform (Int DCT) is the main module which is used for transformation from spatial domain to frequency domain [18]. Integer DCT has been implemented with two different approaches with fully parallel and recursive architecture. The recursive architecture approach uses same 1D DCT modules at different time interval to calculate 2D integer DCT. The fully parallel has two separate 1D integer DCT modules that run parallel to achieve overall 2D integer computation.

The paper is ordered as follows: Section 2 covers the literature survey of transform domain real time video watermarking. The detailed explanation of the proposed real time video watermarking algorithm is provided in section 3 In section 4, the architecture of for hardware implementation is illustrated and two different architectures for Int DCT are explained. Finally, the paper is illustrated with the results analysis of video watermarking algorithm in section 5 and the conclusion is implicated in section 6.

# 2. Related Transform Domain Real Time Video Watermarking

The arena of watermarking has started with image watermarking from past two decades [13]. The research of video watermarking has started a few years back. Earlier video watermarking algorithms were developed based on uncompressed domain and were not targeted for any standard. Then, real time requirement of watermark embedding has been noticed in applications like video broadcasting, Digital Versatile Disk (DVD) copy control, video authentication etc. [2, 14]. The electronics appliances are used to follow the video compression standard. The direction of research is going towards the development of video watermarking algorithm suited for the video standard [23]. Previously, many researchers have attempted transform domain real time watermarking which can be adapted with conventional video coding standard [9]. The real time performance of the algorithm has been defined with computational complexity of architecture. The video watermarking algorithm has evolved for variety of purposes such as copyright protection, proof of authenticity and ownership verification. The algorithm should comprise fundamental requirements like of robustness. imperceptibility, payload and blind detection. The robustness defines the stability of the algorithm against all form of attacks [24]. Imperceptibility signifies the visual distortion present in the content [25]. Payload is the vital parameter which defines the amount of data being embedded in original content with consideration of imperceptibility and robustness. Blind detection is useful to retrieve the watermark from the watermarked video without the access of original content.

Petitjean *et al.* [16] designed fractal coding based video watermarking for digital video compliance system. The work was useful for transform domain real time hardware implementation. The method was designed for MPEG-2 video compression standard. The algorithm was optimized and implemented on DSP, Very Long Instruction Word (VLIW) processor and subsequently prototyped on FPGA platform.

Vural *et al.* [26] introduced blind video watermarking for digital cinema using Discrete Wavelet Transform (DWT). The method was used to embed the watermark in low frequency coefficients of the frame in the video. The frame for watermark embedding was selected randomly using the hash function and the watermarking was performed to secure the content at the transmitter as well as at the receiver end. The payload of 256 bytes was embedded in the fifth level of wavelet sub band of 512×512 Lena image.

Mohanty *et al.* [15] presented perceptual based adaptive watermarking algorithm for video broadcasting system. This paper described VLSI architectures of DCT based real-time watermarking suited for MPEG-4 compression standard. The architecture was prototyped on Altera Cyclone II FPGA using VHDL.

Roy *et al.* [20] developed hardware architecture for semi fragile video watermarking on real time video authentication in surveillance camera. The proposed video algorithm was based on DCT method and could work as embedding chip for MJPEG video compression. The algorithm was tested with different frame size and simulated with Verilog hardware description language.

All previous transform domain video watermarking methods were based on MPEG video watermarking and insert perceptual and/or semi fragile watermark. MPEG and all prior video compression standards use the conventional floating path DCT implementation corresponding based [8]. The MPEG video watermarking schemes require heavy computational complexity because involvement of floating data structure therefore they are not useful in real time implementation. The proposed video watermarking scheme is mainly designed to have compatibility with integer arithmetic.

# 3. Proposed Real-Time Video Watermarking

Proposed video algorithm is based on H.264 video compression standard which uses integer DCT for transformation [11]. Each frame of a video is divided in the number of 8x8 blocks for 2D integer DCT [4]. In the paper, two different architectures of Integer DCT are developed for better speed and area. The algorithm uses a scene change detection technique for watermark embedding. This embedding method has the advantage against temporal attacks where loss of number of frames will not destroy the watermark.

#### Process of Embedding the Watermark:

*Input: Original video, 8 bit per pixel watermark. Output: Secured watermarked video.*

- Step 1: Original uncompresses (.yuv form) video is divided in the group frames using histogram difference method in order to detect the change of a scene.

- Step 2: Each frame from a group is processed by 8×8 block to compute the 2D Integer DCT.

- Step 3: The original watermark (i.e., a image in our experiments) is separated in the eight different planes. Each plane represents the part of original watermark and is treated as one watermark.

- Step 4: The different planes of a particular watermark are embedded in the subsequent frames of a particular group of video.

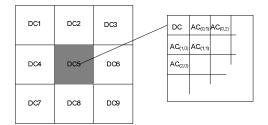

- Step 5: There will be large correlation among the frames of the video. The AC values can be estimated through DC values of

the surrounding blocks as shown in Figure 1. AC values are predicted with help of Equations 1-5 as follows:

Figure 1. Prediction of AC values.

$$AC'_{(0,1)} = |9*temp1| >> 6$$

(1)

$$AC'_{(1,0)} = |9*temp2| >> 6$$

(2)

$$AC'_{(0,2)} = |temp 3 - 2 * DC_5| >> 5$$

(3)

$$AC'_{(2,0)} = |temp 4 - 2*DC_5| >> 5$$

(4)

$$AC'_{(1,1)} = 3* |temp 5 - temp 6| >> 7$$

(5)

Where  $temp1=(DC_4-DC_6)$ ,  $temp2=(DC_2-DC_8)$ ,  $temp3=(DC_4-DC_6)$ ,  $temp4=(DC_2+DC_8)$ ,  $temp5=(DC_1+DC_9)$ , and  $temp6=(DC_3+DC_7)$ .

- Step 6: To predict the AC values, simple arithmetic operations are used as shifting, addition/ subtraction and multiplication. Proposed watermark embedding algorithm has the integer arithmetic which is suitable for integer DCT.

- Step 7: The estimated values AC' are compared with original values obtained in Step 2. The small change in the form of  $\Delta$  is added to original AC values according to the watermark.

If watermark bit = 1

then

$$AC_i \ge AC'_i + \Delta$$

else

$AC_i \ge AC'_i - \Delta$

(6)

Process of Retrieving the Watermark:

*Input: Secure Watermarked video. Output: Retrieved watermark image.*

- Step 1: According to scene change detection method, the secure watermarked video is again separated in the different groups of frames.

- Step 2: Each frame from same group of the scene is transformed using 2D Int DCT. These values are used for the estimation of 5 AC coefficients with above Equations 1-5 in the embedding process.

- Step 3: For retrieval of the watermark, original AC values are compared with the estimated values as follows.

$$if AC \ge AC'_{i}$$

$$Watermark \ bit=1$$

$$else$$

$$Watermark \ bit=0$$

(7)

Step 4: With the retrieval of a bit, the watermark is constructed using different bit planes.

## 4. Real Time Implementation of Proposed H.264 based Video Watermarking

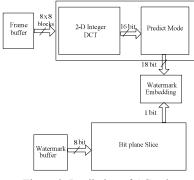

Proposed H.264 based video watermarking is divided in two different and independent process as watermark processing and original frame processing. The architecture of the watermark algorithm is designed to have real time performance as represented in Figure 2. In the subsequent section, the detailed implementations of the modules are explained.

Figure 2. Prediction of AC values.

#### 4.1. Implementation of Integer 2-D DCT

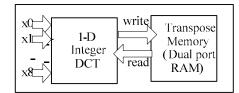

The original frames are stored in the frame buffer according to scene change detection. 2D DCT is executed with separable property. 1D DCT is calculated first with column processing and next time it is calculated with same manner for row processing. 2D DCT architecture has been implemented with two different approaches. In first recursive architecture, same 1D DCT is used for both column and row transformation. The transformed values of column DCT are stored and then applied to same 1D DCT for row transformation as shown in Figure 3.

Figure 3. 2-D integer DCT with recursive architecture.

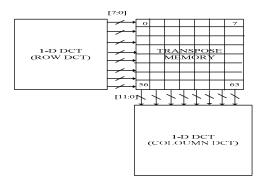

In second approach of full parallel architecture, two separate 1D DCT work in parallel as revealed in Figure 4. Dual port RAM is used as transpose memory to perform transposition operation where data are written in column manner and read in row wise. 1D Int DCT is computed with help of fast butterfly structure. At every clock cycle, 8×8 blocks of original frame have been read and processed from frame buffer.

Figure 4. 2D integer DCT with fully parallel architecture.

#### 4.2. Implementation of Prediction Module

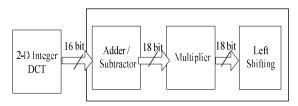

The output of 2D DCT is applied to prediction module for the estimation of AC values which are further used during watermark embedding process. The values are predicted after one clock cycle delay through operations such as addition/subtraction, multiplication and shifting as shown in Figure 5. The predicted values AC' are used to compare with original AC values. According to a watermark bit, the small delta  $\Delta$  (between 2 to 5) is added to generate watermarked frame.

Figure 5. 2-D integer DCT fully parallel architecture.

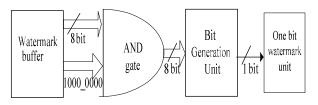

#### 4.3. Implementation of Bit Plane Slice Module

It is used to generate one bit watermark. It works in pipelining manner and is operated independently with respect to Integer 2D DCT and prediction process. The original watermark is processed from watermarked buffer. The values are used to perform bitwise AND operation with stored registered value of 1000\_0000 as described in Figure 6. The output is compared with zero in order to generate one bit value. If the output is greater than zero then the watermark bit is one otherwise the watermark bit is zero. The generated watermark bit is embedded in a frame of the video.

Figure 6. Bit plane slice architecture.

#### 5. Results and Analysis

The performance is quantified with standard quality parameter such as Peak Signal to Noise Ratio (PSNR) and Mean Square Error (MSE) measurement.

$$MSE = \begin{pmatrix} \sum_{m=1}^{M} \sum_{n=1}^{N} \left| p(m,n) - q(m,n) \right|^{2} \\ M \times N \end{pmatrix}$$

(7)

Where p(m, n)= pixel values of p frame, q(m, n)= pixel value of q frame. *M*=frame size of p, *N*=frame size of q.

$$PSNR = 10 \log_{10} \left( \frac{(2^{k} - 1)^{2}}{MSE} \right)$$

(8)

Where k= number of bit required to represent one pixel value.

For the simulation, "carphone.yuv" (frame size  $144 \times 176$ ) is considered as original test video and 'peppers.png' (frame size  $32 \times 32$ ) image is used as the original watermark, which are displayed in Figures 7-a and b respectively. The secure video after the embedding of watermark is shown in Figure 7-c.

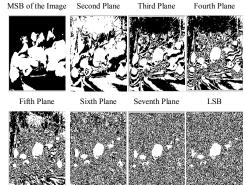

Figure 8. Different Planes of original watermark.

The eight different planes (MSB plane to LSB plane) of the original watermark are represented in Figure 8. MSE is the measurement of errors between two frames. PSNR is the logarithmic function and has inverse relation with MSE. In absence of an attack, average PSNR and MSE between original and watermarked frames of the video are around 54.274 and 0.243 respectively. The resulted values clarify the imperceptibility criterion of the watermark embedding process. The robustness of the proposed algorithm is quantified with Normalized Correlation (NC). NC is correlation between two frames and is calculated as follows.

$$NC(w,w') = \frac{\sum_{i=1}^{k-1} W \times W'}{\sqrt{\sum_{i=1}^{k-1} W^2} \sqrt{\sum_{i=1}^{k-1} W^2}}$$

(9)

Where *W*=original watermark, *W*'=extracted watermark, and *k*=size of watermark.

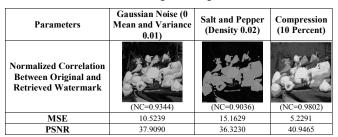

The simulation results are obtained on MATLAB platform. The algorithm is tested against all the temporal attacks and results are reported in the form of NC as shown in Table 1. Some of the image based attacks are also considered for the particular frames and the performance of the algorithm is defined in Table 2. The minimum observed value of NC after retrieval of the watermark is around 0.87 which is quite good for any watermarking algorithm.

Table 1. Performance of algorithm against various temporal attacks.

| Attacks            | <b>Retrieved Watermark</b> | <b>Retrieved Watermark</b> | <b>Retrieved Watermark</b> |

|--------------------|----------------------------|----------------------------|----------------------------|

| Frame<br>Dropping  | 10 Percentage              | 20 Percentage              | 30 Percentage              |

|                    | (NC= 0.9862)               | (NC = 0.9802)              | (NC=0.8765)                |

| Frame<br>Swapping  | 10 Percentage              | 20 Percentage              | 30 Percentage              |

|                    | (NC=0.9980)                | (NC=0.9928)                | (NC=0.9850)                |

| Frame<br>Averaging | 10 Percentage              | 20 Percentage              | 30 Percentage              |

|                    | (NC=0.9979)                | (NC=0.9432)                | (NC=0.9321)                |

Table 2. Performance of algorithm against standard attacks.

In Table 2, MSE and PSNR are calculated between original frame and watermarked fame of the video. The lesser value of MSE indicates the imperceptibility of the proposed algorithm. From the experimental results obtained in Tables 1 and 2, the attained values signify the admirable performance of the proposed scheme. The algorithm poses the greater robustness against all the forms of attacks because of introduction of scene change detection method. The modules of the proposed methods have been synthesized with design compiler tools with 0.18 um Faraday library. The resultant area and power of all the required modules are noted in the Table 3 shown below.

Table 3. Synthesis results of the modules for the proposed watermark algorithm.

| Modules                                     | Area (µm <sup>2</sup> ) | Power (mw) |

|---------------------------------------------|-------------------------|------------|

| 2-D Integer DCT Recursive Architecture      | 23998.00                | 196.90     |

| 2-D Integer DCT Fully Parallel Architecture | 30115.00                | 255.19     |

| Prediction Stage                            | 951.00                  | 6.65       |

| Bit Plane Slice                             | 192.00                  | 0.023      |

Previous works of transform domain watermarking were based mainly on the MPEG based compression standard. Petitjean *et al.* [16] realized an watermarking method based on MPEG-2 standard which used general DCT method. Due to the involvement of floating point arithmetic, the architecture complexity increases and the performance of real time decreases. Vural *et al.* [26] designed watermarking scheme in frequency domain using wavelet transform but all the present standards imbibe DCT module for its transformation. Mohanty *et al.* [15] suggested the

perceptual watermarking architecture for MPEG-4 application but it also requires the floating values in data path. This avoids the integration of the watermarking unit with H.264 standard which has mainly integer arithmetic.

Roy et al. [20] presented DCT based video watermarking for MJPEG standard. This algorithm embeds the semi fragile watermark which is used to detect any form of tempering for the frames of a video. The semi fragile watermarking has the feature that the watermark is capable to withstand some primary attacks while it demolishes in case of severe attacks beyond certain limit. The architecture requires heavy computational demands due to floating point operation. All the works defined in the past literatures were not robust against all attacks and is not useful as proof of ownership or not helpful any more as a court evidence. The proposed algorithm posses robustness against all the attacks and used to provide the authenticity. The proposed algorithm is compared with other real time transform domain video watermarking in Table 4. Two different architecture of 2D DCT are designed to have optimized results in area and speed respectively. Recursive approach of algorithm has better results for factors like area and power but suffers in terms of speed due to folded separable property of 2D DCT module. In the second fully pipeline design approach, the speed is achieved at the expense of area. The integer DCT unit has huge area because of the larger amount of memory requirement for the storage of original frame values and their transform values.

Table 4. Comparison watermarking architecture with previous work.

| Research<br>Work                      | Watermark<br>Type         | Domain         | Standard | Frame<br>Size  | Results                                                                            |

|---------------------------------------|---------------------------|----------------|----------|----------------|------------------------------------------------------------------------------------|

| Petitjean <i>et al</i> . [16]         | Robust                    | Fractal        | MPEG-2   |                | 6 μs for FPGA (50<br>MHz)<br>78 μs for Pentium III<br>118 μs for VLIW<br>(250 MHz) |

| Vural <i>et al</i> . [26]             | Invisible<br>Robust       | DWT            | MPEG     | 512×512        | NA                                                                                 |

| Mohanty <i>et al</i> . [15]           | Visible                   | DCT            | MPEG-4   | 320×240<br>x 3 | 100 MHz                                                                            |

| Roy et al. [20]                       | Invisible<br>Semi Fragile | DCT            | MJPEG    | 640×480        | 0.18µ,10 mW,<br>40 MHz                                                             |

| Proposed (Recursive<br>Approach)      | Invisible<br>Robust       | Integer<br>DCT | H.264    | 720×486        | 0.18μ,2.55 mm <sup>2</sup> ,<br>48.25 mW,37 MHz                                    |

| Proposed (Fully<br>Parallel Approach) | Invisible<br>Robust       | Integer<br>DCT | H.264    | 720×486        | 0.18μ,3.20 mm <sup>2</sup> ,<br>62.5 mW,120 MHz                                    |

#### 6. Conclusions

Parallel and pipeline architecture of the proposed video algorithm has been developed with Integer DCT implementation. The embedding process uses two different integer DCT architectures, one is Recursive DCT architecture and other is fully parallel architecture, with area and speed optimization for desired application. The proposed scheme has designed to adapt H.264 standard. The introduction of scene change detection concept has improved the performance significantly against temporal attacks.

# References

- [1] Belghith F., Loukil H., and Masmoudi N., "Efficient Hardware Architecture of a Modified 2-D Transform for the HEVC Standard," *International Journal of Computer Science and Application*, vol. 2, no. 4, pp. 59-69, 2013.

- [2] De Strycker L., Termont P., Vandewege J., Haitsma J., Kalker M., Maes M., and Depovere G., "Implementation of a Real-Time Digital Watermarking Process for Broadcast Monitoring on Trimedia VLIW Processor," *in Proceedings of IEEE on Vision, Image and Signal Processing*, IET pp. 371-376, 2007.

- [3] Dias T., López S., Roma N., and Sousa L., "Scalable Unified Transform Architecture for Advanced Video Coding Embedded Systems," *International Journal of Parallel Programming*, vol. 41, no. 2, pp. 236-260, 2013.

- [4] Edirisuriya A., Madanayake A., Dimitrov S., Cintra J., and Adikari J, "VLSI Architecture for 8-Point AI-DCT having Low Area-Time Complexity and Power at Improved Accuracy," *Journal of Low Power Electronics and Applications*, vol. 2, no. 2, pp. 127-142 ,2012.

- [5] Joshi A., Mishra V., and Patrikar M., *Real Time Implementation of Digital Watermarking Algorithm for Image and Video Application*, 2012.

- [6] Jridi M., Ouerhani Y., and Alfalou A., "Low Complexity DCT Engine for Image and Video Compression," available at: https://hal.archivesouvertes.fr/hal-00783020/document, last visited 2013.

- [7] Kougianos E., Mohanty P., and Mahapatra N., "Hardware Assisted Watermarking for Multimedia," *Computers and Electrical Engineering*, vol. 35, no. 2, pp. 339-358, 2009.

- [8] Maes M., Kalker T., Linnartz P., Talstra J., Depovere G., and Haitsma J., "Digital Watermarking for DVD Video Copyright Protection," *IEEE Signal Processing Magazine*, vol. 17, no. 5, pp. 47-57, 2000.

- [9] Mahmoud W., Datta S., and Flint A., "Frequency Domain Watermarking: An Overview," *the International Arab Journal of Information and Technology*, vol. 2, no. 1, pp. 33-47, 2005.

- [10] Malvar S., Hallapuro A., Karczewicz M., and Kerofsky L., "Low-Complexity Transform and Quantization in H.264/AVC," *IEEE Transactions* on Circuits and Systems for Video Technology, vol. 13, no. 7, pp. 598-603, 2003.

- [11] Martuza M. and Wahid A., "Low Cost Design of a Hybrid Architecture of Integer Inverse DCT for H.264, VC-1, AVS, and HEVC," VLSI Design -Special issue on VLSI Circuits, Systems, and Architectures for Advanced Image and Video Compression Standards, vol. 2012, no. 2, pp. 1-10, 2012.

- [12] Masoumi M. and Amiri S. "Content Protection in Video Data Based on Robust Digital

Watermarking Resistant to Intentional and Unintentional Attacks," *the International Arab Journal of Information and Technology*, vol. 1, no. 2, pp. 204-212, 2014.

- [13] Mathai J., Kundur D., and Sheikholeslami A., "Hardware Implementation Perspectives of Digital Video Watermarking Algorithms," *IEEE Transactions on Signal Processing*, vol. 51, no. 4, pp. 925-938, 2003.

- [14] Mathai J., Sheikholeslami A., and Kundur D., "VLSI Implementation of a Real-Time Video Watermark Embedder and Detector," *in Proceedings of the International Symposium on Circuits and Systems*, pp. 772-775, 2003.

- [15] Mohanty P., Kougianos E., Cai W., and Ratnani M., "VLSI Architectures of Perceptual Based Video Watermarking for Real-Time Copyright Protection," in Proceedings of the 10<sup>th</sup> International Symposium on Quality of Electronics Design, San Jose, California, pp. 527-535, 2009.

- [16] Petitjean G., Dugelay L., Gabriele S., Rey C., and Nicolai J., "Towards Real-Time Video Watermarking for System-on-Chip," in Proceedings of IEEE International Conference on Multimedia and Expo, pp. 597-600, 2002.

- [17] Piva A., Bartolini F., and Barni M., "Managing Copyright in Open Networks," *IEEE Transaction on internet computing*, vol. 6, no. 3, pp. 18-26, 2002.

- [18] Rajapaksha N., Edirisuriya A., Madanayake A., Cintra J., Onen D., Amer I., and Dimitrov S., "Asynchronous Realization of Algebraic Integer-Based 2D DCT Using Achronix Speedster SPD60 FPGA," *Journal of Control Science and Engineering*, vol. 2013, no. 1, pp.1-9, 2013.

- [19] Richardson E., *H.264 and MPEG-4 Video Compression: Video Coding for Next Generation Multimedia*, John wiley and Sons, 2003.

- [20] Roy D., Li X., Shoshan Y., Fish A., and Yadid-Pecht O., "Hardware Implementation of a Digital Watermarking System for Video Authentication," *IEEE Transaction on Circuit and Systems for Video Technology*, vol. 23, no. 2, pp. 289-301, 2011.

- [21] Shoshan Y., Fish A., Jullien. A., and Yadid-Pecht O., "Hardware Implementation of a DCT Watermark for CMOS Image Sensors," in Proceedings of 15<sup>th</sup> IEEE International Conference Electronics, Circuits and Systems, Julien's, pp. 368-371, 2008.

- [22] Stutz T. and Uhl A., "A Survey of H.264 AVC/SVC Encryption," *IEEE Transaction on Circuits and Systems for Video Technology*, vol. 22, no. 3, pp. 325-339, 2012.

- [23] Tsai H. and Wu Y., "An Implementation of Configurable Digital Watermarking Systems in MPEG Video Encoder," in Proceedings of IEEE International Conference on Consumer Electronics, pp. 216-217, 2003.

- [24] Voloshynovskiy S., Pereira S., Pun T., Eggers J., and Su K., "Attacks on Digital Watermarks: Classification, Estimation based Attacks and Benchmarks," *IEEE Communications Magazine*, vol. 39, no. 8, pp. 118-126, 2001.

- [25] Vundela P. and Sourirajan V., "A Robust Multiwavelet-Based Watermarking Scheme for Copyright Protection of Digital Images Using Human Visual System," *the International Arab Journal of Information and Technology*, vol. 10, no. 6, pp. 527-535, 2013.

- [26] Vural S., Tomii H., and Yamauchi H., "Video Watermarking for Digital Cinema Contents," in Proceedings of the 13<sup>th</sup> European Signal Processing Conference, pp. 303-304, 2005.

- [27] Wiegand T., Sullivan J., Bjontegaard G., and Luthra A., "Overview of the H.264/AVC Video Coding Standard," *IEEE Transaction for Circuits* and Systems for Video Technology, vol. 13, no. 7, pp. 560-576, 2003.

- [28] Zhang D., Li B., Xu J., and Li H., "Fast Transcoding from H. 264 AVC to High Efficiency Video Coding," in Proceedings of IEEE International Conference on Multimedia and Expo, Melbourne, Australian, pp. 651-656, 2012.

Amit Joshi Amit Joshi received his Bachelor of Engineering (B.E.) degree of Electronics in 2005 from Veer Narmad South Gujarat University (VNSGU), Surat, India and Master of Technology (M.Tech.) degree from Sardar

Vallbhbhai National Institute of Technology (SVNIT), Surat in 2009. Currently, He is working as Assistant at Electronics and Communication Professor Department, Malaviya National Institute of Technology (MNIT), Jaipur, India. He has completed his PhD degree from Sardar Vallbhbhai National Institute of Technology (SVNIT), Surat. He has six years of teaching experience and two years of industry experience. His current research interest includes: Hardware implementation of data security algorithms, Architecture level synthesis of various signal processing applications, FPGA based design etc.. He is member of IEEE, Associate member of IET, and member of IETE.

**Vivekanand Mishra** has done his PhD degree in Optical Communication and Optical Waveguide in the year 2001 from IIT, B.H.U. After completing his PhD degree he served as an academician for nine years in

different university of Malaysia as well as he was Research consultant in Telecom Malaysia Research and Development. Presently he is serving as an Associate Professor, Department of Electronics Engineering and also serving as a Research Dean, S.V. National institute of Technology, Surat. His research involve areas related interests to: Optical communications, optical sensor, and nonlinear optics. He has published more than 100 research papers till now in various reputed Journals of SCI and ISI indexed and he has also published one book in John Wiley publisher a delivered many expert talk and workshops at various institutes. He is an active senior member of IEEE, Fellow IETE also he served as secretary of Institute of Photonics Research and Application (IPRA) and Optical communication group (OCG), MMU Malaysia. He is also a reputed reviewer of DST proposals.

**Rajendra Patrikar** is working presently as Professor of Electronics at VNIT Nagpur. He has done his MTech and PhD degrees in electrical engineering from IIT Bombay. He joined as faculty at IIT Bombay after working for a year at Computer

vision RandD Pune. Later he moved to Singapore and worked in TECH Semiconductor in Advance Device Technology Department (1998-2000). After working there for three years he moved to Institute of High Performance Computing, Singapore which is a supercomputing centre (2001-2003). He was a Team Leader of Nanotechnology group at Computational Research Laboratory Pune (Super computing centre by TATAs) for one Year. He has published more than 25 papers in International Journals and 80 papers in refereed conferences. He is a Fellow of IETE, Senior member of IEEE and Member of SPIE.